Product Summary

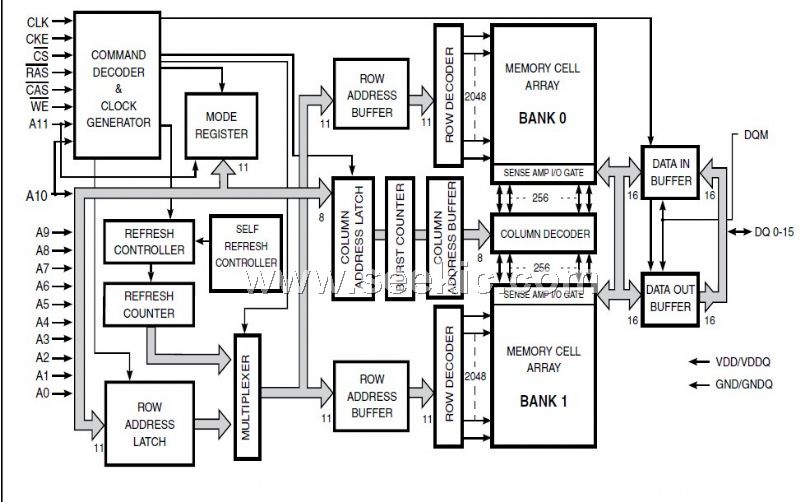

ISSI’s 16Mb Synchronous DRAM IS42/4516100E is

organized as a 524,288-word x 16-bit x 2-bank for

improved performance. The synchronous DRAMs

achieve high-speed data transfer using pipeline

architecture. All inputs and outputs signals refer to the

rising edge of the clock input.

Features

? Clock frequency: 200, 166, 143 MHz

? Fully synchronous; all signals referenced to a

positive clock edge

? Two banks can be operated simultaneously and

independently

? Dual internal bank controlled by A11 (bank select)

? Single 3.3V power supply

? LVTTL interface

? Programmable burst length

– (1, 2, 4, 8, full page)

? Programmable burst sequence:

Sequential/Interleave

? 2048 refresh cycles every 32ms (Com, Ind, A1

grade) or 16ms (A2 grade)

? Random column address every clock cycle

? Programmable CAS latency (2, 3 clocks)

? Burst read/write and burst read/single write

operations capability

? Burst termination by burst stop and

precharge command

? Byte controlled by LDQM and UDQM

? Packages: 400-mil 50-pin TSOP-II and 60-ball

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

IS42S16100E-7TL |

ISSI |

DRAM 16M (1Mx16) 143Mhz SDRAM, 3.3v |

Data Sheet |

|

|

||||||||||||

|

IS42S16100E-7TL-TR |

ISSI |

DRAM 16M (1Mx16) 143Mhz SDRAM, 3.3v |

Data Sheet |

|

|

||||||||||||

|

IS42S16100E-7TLI-TR |

ISSI |

DRAM 16M (1Mx16) 143MHz SDRAM, 3.3v |

Data Sheet |

|

|

||||||||||||

|

IS42S16100E-7TLI |

ISSI |

DRAM 16M (1Mx16) 143MHz SDRAM, 3.3v |

Data Sheet |

|

|

||||||||||||

(Hong Kong)

(Hong Kong)