Product Summary

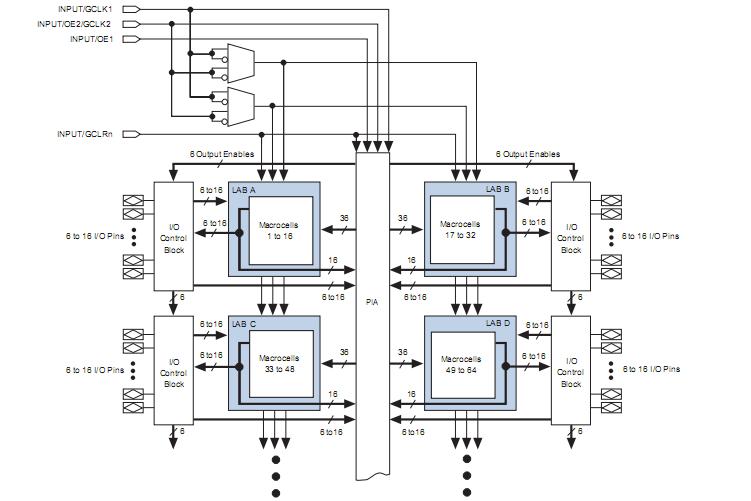

The EPM7160EQC160-20 high-density, high-performance PLD is based on Alteras second-generation MAX architecture. Fabricated with advanced CMOS technology, the EPM7160EQC160-20 provides 600 to 5,000 usable gates, ISP, pin-to-pin delays as fast as 5 ns, and counter speeds of up to 175.4 MHz. The EPM7160EQC160-20 contains from 32 to 256 macrocells that are combined into groups of 16 macrocells, called logic array blocks(LABs). Each macrocell has a programmable-AND/fixed-OR array and a configurable register with independently programmable clock, clock enable, clear, and preset functions.

Parametrics

EPM7160EQC160-20 absolute maximum ratings: (1)Supply voltage With respect to ground: –2.0 to 7.0 V; (2)DC input voltage: –2.0 to 7.0 V; (3)DC output current, per pin: –25 to 25 mA; (4)Storage temperature No bias: –65 to 150 ℃; (5)Ambient temperature Under bias: –65 to 135 ℃; (6)Junction temperature Ceramic packages, under bias: 150 ℃, PQFP and RQFP packages, under bias: 135 ℃.

Features

EPM7160EQC160-20 features: (1)Includes 5.0-V MAX 7000 devices and 5.0-V ISP-based MAX 7000S devices; (2)Built-in JTAG boundary-scan test (BST) circuitry in MAX 7000S devices with 128 or more macrocells; (3)Complete EPLD family with logic densities ranging from 600 to 5,000 usable gates (see Tables 1 and 2); (4)5-ns pin-to-pin logic delays with up to 175.4-MHz counter frequencies (including interconnect); (5)PCI-compliant devices available; (6)Open-drain output option in MAX 7000S devices; (7)Programmable macrocell flipflops with individual clear, preset, clock, and clock enable controls; (8)Programmable power-saving mode for a reduction of over 50% in each macrocell; (9)Configurable expander product-term distribution, allowing up to 32 product terms per macrocell.

Diagrams

(Hong Kong)

(Hong Kong)